### Ecole Normale Supérieure de Cachan

61 avenue du président Wilson 94230 CACHAN

Concours d'admission en 3<sup>ème</sup> année GÉNIE ÉLECTRIQUE Session 2011

# Épreuve de TECHNIQUES NUMÉRIQUES ET AUTOMATIQUE

| Durée : <b>4 heures</b>        |  |

|--------------------------------|--|

|                                |  |

|                                |  |

| Aucun document n'est autorisé. |  |

|                                |  |

|                                |  |

|                                |  |

L'usage de calculatrices électroniques de poche à alimentation autonome, non imprimantes et sans document d'accompagnement, est autorisé selon la circulaire n°99018 du 1<sup>er</sup> février 1999. De plus, une seule calculatrice est admise sur la table, et aucun échange n'est autorisé entre les candidats. »

Si, au cours de l'épreuve, un candidat repère ce qui lui semble être une erreur d'énoncé, il le signale sur sa copie et poursuit sa composition en expliquant les raisons des initiatives qu'il est amené à prendre.

L'épreuve est constituée de 2 parties indépendantes (techniques numériques et automatique) qui doivent être obligatoirement traitées et rédigées sur des copies séparées.

## Problème A

( Durée : 2 heures

## <u>Techniques numériques</u> <u>Implantation d'une détection synchrone dans un FPGA</u>

#### A.1 Présentation

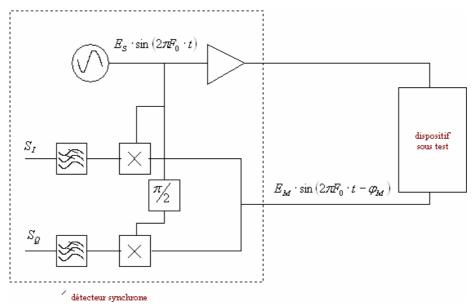

La détection synchrone est une technique de mesure largement utilisée en instrumentation (mesure d'impédance, capteurs inductifs, capteurs à courants de Foucault, resolver, etc...). Le principe général en est rappelé en figure 1. les filtres passe-bas sont souvent des intégrateurs. Il s'agit de mesurer  $E_M$  et  $\varphi_M$ .

figure 1 : principe de la détection synchrone

**Question 1)** Donner les expressions de  $S_I$  et  $S_Q$  et le traitement qu'il faudra faire sur ces signaux pour déterminer  $E_M$  et  $\varphi_M$

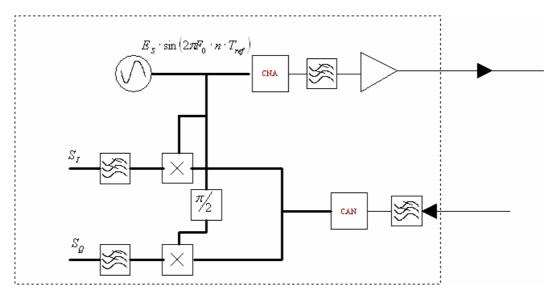

Il existe depuis longtemps des détections synchrones intégrées comprenant l'oscillateur de référence, les multiplieurs et les filtres passes bas. La technologie permet aujourd'hui de réaliser des détections synchrones numériques qui bénéficient de l'avantage de pouvoir intégrer des traitements algorithmiques et des interfaçages de type réseau (figure 2)

$figure\ 2: détecteur\ synchrone\ numérique\ (les\ traits\ épais\ représentent\ des\ mots\ binaires\ )$

Question 2) Quels rôles jouent les filtres en amont du CAN et aval du CNA?

#### A.2 Oscillateur numérique (NCO)

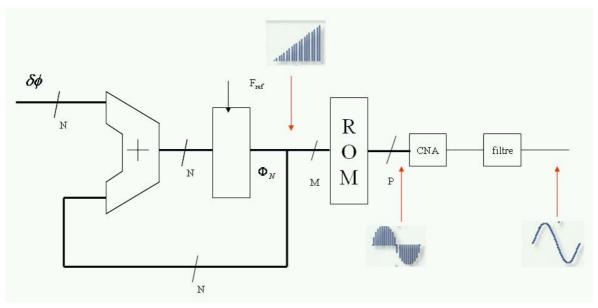

Il s'agit d'élaborer les échantillons  $E_S \cdot \cos(2\pi F_0 \cdot n \cdot T_e)$  de la sinusoïde de référence. Le principe utilisé est celui de la synthèse numérique directe (Direct Digital Synthesis ou DDS), donné en figure 3

Un registre de N bits est incrémenté, modulo  $2^N$ , d'une quantité  $\delta \phi$  à chaque période de l'horloge  $F_{ref}$ . Le mot constitué des M bits (M<N) de plus fort poids de ce registre,  $\Phi_M = \Phi_N \cdot 2^{M-N}$ , est appliqué en entrée d'une 'ROM sinus' de P bits, qui réalise ainsi la fonction :

$$\sin\left(2\pi\cdot\frac{\Phi_{M}}{2^{M}}\right)\cdot2^{P-1}$$

Ce mot est appliqué à un convertisseur numérique analogique de P bits, puis filtré.

figure 3 : principe de la synthèse numérique directe (DDS)

**Question 3**) En prenant  $F_{ref}$ = 40 MHz, N=10, M=P=8,  $\delta \varphi$ =195, donner les valeurs successives de M en entrée de la ROM, P en entrée du CNA et tracer le signal en sortie du CNA pour les 20 premiers échantillons (le registre est initialement à 0)

**Question 4**) Donner l'expression de la fréquence du signal généré  $F=f(\delta \varphi, N, M, P, F_0)$ .

**Question 5**) Quelles sont les influences des paramètres M et P?

Question 6) Quel est le pas de réglage de la fréquence ?

**Question 7**) En reprenant les valeurs de Question 3), tracer les spectres du signal généré en entrée et sortie du CNA.

Question 8) Quelles doivent être les caractéristiques du filtre qui suit le CAN?

Question 9) Quelle est la plage de fréquence que l'on peut générer avec cette structure dans le cas général

La détection synchrone a besoin de disposer des échantillons  $E_S \cdot \sin(2\pi F_0 \cdot n \cdot T_e)$  et  $E_S \cdot \sin(2\pi F_0 \cdot n \cdot T_e)$ , quelque soit  $F_0$ .

**Question 10**) Proposer une modification de la structure de la figure 3 permettant d'obtenir les 2 échantillons tout en utilisant une seule ROM.

Dans la suite on prend  $F_{ref}=40 \text{ MHz}$ , N=32, M=12, P=16 et  $\delta \varphi_0 = 1073152$ .

**Question 11**) Donner la fréquence  $F_0$  ainsi générée.

**Question 12**) Donner les 5 premiers mots de la ROM 'sinus'

#### A.3 <u>Détection synchrone</u>

#### A.3.a Echantillonnage, intégration

Il n'est pas nécessaire d'échantillonner le signal  $E_M \cdot \sin(2\pi F_0 \cdot t - \varphi_M)$  à la fréquence  $F_{ref}$  du DDS. On choisit donc de faire fonctionner le CAN (16 bits) à une fréquence d'échantillonnage  $F_e = \frac{F_{ref}}{256}$ . On obtient ainsi une séquence d'échantillons  $\{E_M \cdot \sin(2\pi F_0 \cdot n \cdot T_e - \varphi_M)\}$  que l'on multipliera par  $\{\sin(2\pi F_0 \cdot n \cdot T_e)\}$  et  $\{\cos(2\pi F_0 \cdot n \cdot T_e)\}$  (obtenus en prenant un échantillon sur 256 en sorties du DDS) pour obtenir  $\{S_1(n \cdot T_e)\}$  et  $\{S_2(n \cdot T_e)\}$ . On effectue l'intégration numérique (c'est-à-dire la somme) de 8192 échantillons successifs.

Question 13) Quelle est la durée de l'intégration

Question 14) Montrer qu'elle contient un nombre entier de périodes des signaux en sortie des multiplieurs

**Question 15**) En déduire ce que représentera les 2 sommes obtenues.

#### A.3.b Implantation dans un FPGA

Les FPGA actuels contiennent des multiplieurs câblés 18x18->36 bits, utilisant la représentation en complément à 2. Les échantillons élaborés par DDS et du CAN sont sur 16 bits.

**Question 16**) Comment étendre la représentation de 16 à 18 bits, sans modifier les valeurs représentées.

Question 17) Quelle est la plage couverte par un produit?

On accumule 8192 produits successifs.

Question 18) Quelle doit être la taille minimum (en nombre de bits) de l'accumulateur?

Il faut calculer en fait

$$M_i = \frac{1}{8192} \cdot \sum_{n=0}^{8191} S_i (n \cdot T_e)$$

(avec  $i = 1$  ou 2).

Question 19) Quelle opération implantable dans un FPGA permet d'obtenir le résultat souhaité.

On suppose que la description VHDL de la détection synchrone utilise un signal déclaré par :

signal ACCU : bit\_vector(64 downto 0)

**Question 20**) Donner la description qui permettra d'élaborer  $M_i$  à partir de ACCU

# PROBLÈME B

DURÉE: 2 heures

# **AUTOMATIQUE**

Le sujet est composé de 3 pages de texte.

#### Certaines parties du sujet sont fortement indépendantes

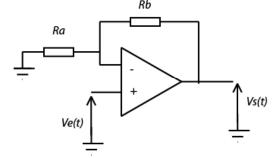

Soit le montage à amplificateur opérationnel (A.Op) suivant :

On considérera l'A.Op. comme idéal, hormis son gain différentiel en boucle ouverte qui sera noté A(p).

# I. Etude du comportement en fréquence d'un amplificateur opérationnel d'usage générale

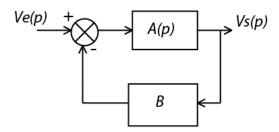

1. Montrer que le montage ci-dessus peut se représenter sous la forme du schéma bloc cidessous. Donner alors l'expression de *B*.

2. Dans le cas où le gain de boucle A(p)\*B est très grand devant 1, donner alors l'expression du gain G du montage complet. Montrer qu'il ne dépend que de Ra et Rb.

1

On se place maintenant dans le cas d'un amplificateur opérationnel classique dont l'expression du gain différentiel est :  $A(p) = \frac{A_0}{1+\pi p}$

3. Calculer la fonction de transfert en boucle fermé : G(p)=Vs(p)/Ve(p).

- 4. Pour G(p), donner l'expression de son gain statique Go et celle de sa bande passante  $\omega_G$  (rad/s).

- 5. Que vaut le produit  $Go * \omega_G$ . Conclure.

On donne  $Ao=10^5$  et  $\tau=0.1$ s.

- 6. Tracer sur le même diagramme, les courbes de Bode (module et argument) de A(p) et de G(p) pour  $B=10^{-1}$  et  $B=10^{-3}$ .

- 7. Que peut-on dire à propos de la stabilité du montage ?

#### II. Montage sur charge capacitive

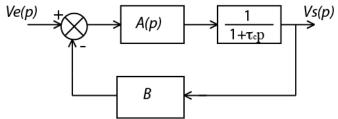

On suppose que le montage précédent est connecté sur une charge capacitive  $C_u$ . On obtient alors comme nouvelle représentation le schéma bloc suivant :

- 1. Proposer une justification de l'introduction de ce nouveau pôle dans le schéma bloc. On prend  $\tau_c$ =100 µs , B=10<sup>-1</sup>. On a toujours Ao=10<sup>5</sup> et  $\tau$ =0,1 s.

- 2. Calculer précisément la marge de phase du montage.

- 3. Que peut-on dire de la réponse à un échelon du montage ?

- 4. Calculer la fonction de transfert en boucle fermée  $G_c(p)$ . La mettre sous la forme :

$$G_c(p) = \frac{G_{co}}{1 + \frac{2m}{\omega_o} p + \frac{p^2}{\omega_o^2}}$$

Donner l'expression et le nom usuellement employé de  $\omega_o$ , m et  $G_{co}$ .

- 5. Donner les valeurs de  $G_{co}$ , m et  $\omega_o$ .

- 6. Tracer alors l'allure du diagramme de bode de  $G_c(p)$  ainsi que sa réponse à un échelon.

- 7. Conclure sur le comportement de l'A.Op. sur charge capacitive.

#### III. Amplificateur opérationnel non compensé

On s'intéresse maintenant au comportement en fréquence d'un amplificateur opérationnel haute performance (appelé amplificateur non compensé). Son gain différentiel en boucle ouverte vaut **50dB** et il présente deux fréquences de coupure à 3 MHz et 60 MHz.

- 1. Donner la fonction de transfert de l'A.Op. en boucle ouverte.

- 2. Tracer sa représentation dans le plan de Black.

- 3. A partir du tracé, donner la marge de phase du système dans le cas d'un retour unitaire.

- 4. A l'aide du tracé, donner la valeur du gain maximal obtenu en boucle fermée pour un retour unitaire. Estimer la fréquence de coupure correspondante.

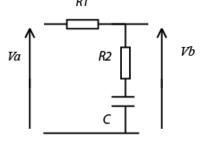

On propose d'étudier un correcteur dit à retard de phase atténuant le profil du gain pour obtenir une marge de phase de 45°. Le montage utilisé pour mettre en place le correcteur est le suivant :

- 5. Donner l'expression de la fonction de transfert C(p)=Vb(p)/Va(p)

- 6. Mettre C(p) sous la forme :  $C(p) = \frac{1 + j\frac{\omega}{\omega_2}}{1 + j\frac{\omega}{\omega_1}}$ . Donner l'expression de  $\omega_1$  et  $\omega_2$

- 7. Tracer l'allure du diagramme dans le plan de Black de C(p). On prendra pour cela  $\omega_2=10*\omega_1$ .

On se place dans le cas d'une chaîne de retour unitaire (B=1). On positionne  $\omega_2$  telle que  $\omega_2$ =2 $\pi^*$ (10.10<sup>6</sup>) rad/s.

- 8. Justifier le choix pour  $\omega_2$ .

- 9. Calculer alors  $\omega_1$  pour que le montage présente un gain de 0dB pour la fréquence 60Mhz. En déduire alors la marge de phase.

- 10. Tracer alors le nouveau diagramme de Black du système ainsi corrigé.

- 11. Que devient la valeur du gain maximal obtenue en boucle fermée pour un retour unitaire.

- 12. Commenter la pertinence de cette correction.

- 13. Proposer un autre principe de correction. Donner sa fonction de transfert associée et justifier votre choix.